Products for which the sale has been cancelled.

- Page

- View all

- 3D print

- Minicomputers

- Electronics

- Sensors

- Robots & mechanics

- Tools & Power Supplies

- Education

- Smart Home

- Others

- 3D PRINTING

- View all

- 3D printers

- Filaments

- Accessories for 3D printers

- Replacement parts for 3D printers

- Creative kits for 3D projects

- Filament dryers

- Postprocessing and filament merging systems

- Resins for 3D printers

- Components for 3D printers construction

- 3D scanners

- 3D Pens

- CNC

- MINICOMPUTERS

- View all

- Raspberry Pi

- Arduino

- Nvidia

- Edge AI

- Flipper Zero

- XIAO

- Odroid

- BBC micro:bit

- Other minicomputers

- M5Stack

- ESP32

- PLC drivers

- ELECTRONICS

- View all

- Computer accessories

- Automobile accessories

- Cooling

- Diodes

- Sound and acoustics

- Mounting components

- Passive elements

- Wearables (e-textiles, smart clothes)

- Cameras

- Consoles

- Memory cards & disks

- Communication

- Converters

- Electronics courses

- Microcontrollers

- Animal repellers

- LED lighting

- Programmers

- Relays

- Voltage regulators

- Artificial intelligence

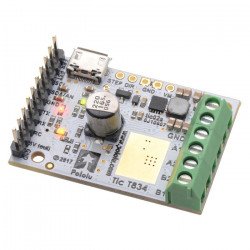

- Motor drivers and servos

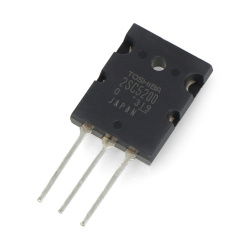

- Integrated circuits

- Displays and screens

- More...

- SENSORS

- View all

- Alarm sensors

- Inductive sensors

- Piezoelectric sensors

- 9DoF IMU sensors

- Pressure sensors

- Oxygen sensors

- Twilight sensors

- Door sensors

- Gas sensors

- Optical sensors

- Tilt sensors

- Accelerometers

- Air quality sensors

- Sound sensors

- Gesture sensors

- Inductive contactless sensors

- Grove modules

- Gravity modules

- Limit switches

- Sensors of light and color

- Magnetic sensors

- Medical sensors

- Pressure sensors

- Sensors odbiciowe

- Distance sensors

- Weather sensors

- Liquid level sensors

- Current sensors

- Flow sensors

- Motion sensors

- Temperature sensors

- PT100 temperature probes

- Humidity sensors

- Fingerprint readers

- Encoders

- Photoresistors

- Hall effect sensors

- RPM sensors

- Phototransistors

- IR receivers

- Magnetometers

- Resistance sensors

- Gyros

- Sensor sets

- More...

- TOOLS AND POWER SUPPLIES

- View all

- Tools

- Soldering

- Power supply

- Oscilloscopes

- Measuring instruments & devices

New products

- New

Promotion products

- Reduced price

- Sale

- Reduced price

- Sale

Withdrawn products

Loading...

JustPi Set of Raspberry Pi 3B+ WiFi + 32GB microSD + accessories

The justPi kit includes a Raspberry Pi 3 mini computer model B+ 1 GB RAM with a protective housing and a 5 V power supply with a current capacity of 2.5 A . A memory...5.0 (23)

Index: RPI-13140

Index: RPI-13140

Discontinued product

i

Unavailable

- Discontinued product

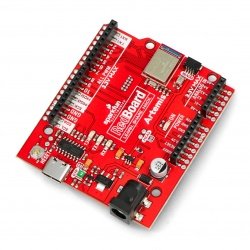

SparkFun RedBoard Artemis - microcontroller board - SparkFun DEV-15444

RedBoard Artemis is a minimalistic SparkFun board equipped with a Bluetooth 5.0 SparkFun Artemis module. The heart of the board is the Artemis chip based on the ARM Cortex...5.0 (1)

Index: SPF-19853

Index: SPF-19853

Discontinued product

i

Unavailable

- Discontinued product

See also

What does the product availability information mean?

- 1. The information displayed on the product page applies to orders placed now. It does not apply to orders placed earlier if a different message was displayed at that time.

- 2. If a specific date is provided, it means that we will begin shipping from our warehouse on that date; this may take 1-2 business days. Shipping may also begin sooner.

- 3. If the date provided is approximate (e.g., only a month), it means the item has been ordered from the manufacturer, but we do not yet know the exact delivery date.

- 4. The dates provided are based on the manufacturer’s estimates, are approximate, and are subject to change.

- 5. Please note that if your order included several unavailable products, we will ship them only once all items are in stock.

- 6. If you want to know the delivery date for an order you’ve already placed, please contact our customer service department.